はじめに

ここでIP coreを含むプロジェクトのシミュレーション方法について説明します.IP(Intellectual Property) coreとは,FPGAなどで再利用可能な回路のコンポーネント情報を指します.例えばFPGAにはブロックRAMが含まれますがそれらを利用するにはIP coreを使ったほうが圧倒的に便利です(というよりもIP coreを使わないと素のVerilogでは書き表すことはほぼ無理です).ここではIP coreを使った場合,シミュレーションするにはどうするのかについて説明します.

環境

以下の環境で開発を行いました.

- FPGA: Gowin GW1NR-9 FPGA

- 開発ボード: Tang Nano 9K を搭載したボード

- 開発環境: Gowin EDA V.1.9.9 Beta-4 Education

IP coreを含むプロジェクトの作成

今回はFPGA内にあるブロックRAMを作成するのにIP coreを利用します.この作成についてはこちらのページにありますので見てください.

シミュレーションの方法

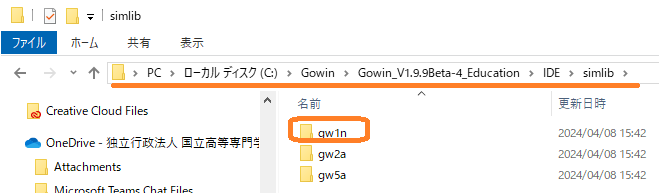

通常のシミュレーションと異なることは,IP coreとして生成されているverilogのファイルが含まれていることです.このverilogには,ブロックRAMのモジュール(SP)が含まれています.このため,このモジュールをシミュレーション時に含めてあげる必要があります.これらのモジュールはGowin EDAのフォルダにありますので,これをソースファイルと同じ所へコピーします.下の図はGowin EDAが含まれるフォルダを表しています.IDEフォルダの下にsimlibというフォルダがあります.今回使用しているFPGAはGW1NRのため,下のようにgw1nフォルダ内のファイルを利用します.

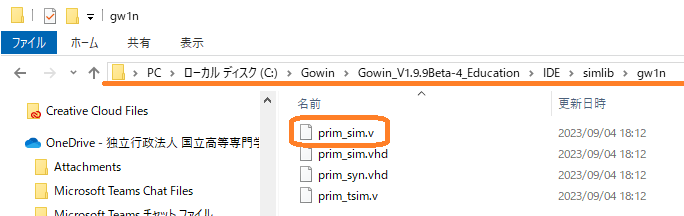

下の図のようにgw1nフォルダを開くと,prim_sim.vファイルがあります.このファイルを他のソースファイルと同じディレクトリへコピーします.

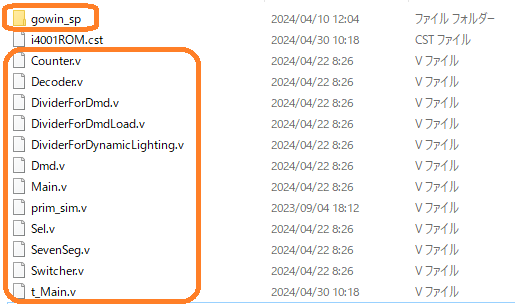

下の図はprim_sim.vファイルを他のソースファイルと同じ所へコピーした様子を表します.この例ではt_Main.vがトップモジュールMainのテストベンチになっています.また,gowin_spフォルダ内にはi4001Block.vというブロックRAMのモジュールが含まれています.

このような場合,iverilogでシンセサイズするには以下のようになります.

iverilog -o Main Main.v gowin_sp/i4001Block.v SevenSeg.v DividerForDmdLoad.v DividerForDmd.v Dmd.v DividerForDynamicLighting.v Counter.v Sel.v Switcher.v Decoder.v prim_sim.v t_Main.v

毎回,上記のようなコマンドを打ち込むのは大変ですので,バッチファイルにしておくことをお勧めします.あとは通常のシミュレーションと同様です.詳しくはこちらをご覧ください.