XC6SLX9をはじめとするSpartan6シリーズにはクロックを管理するDCM(Digital Clock Manager)があり,これによって特定の周波数の方形波を作り出すことができます.この文書ではISEに備わるIP(CORE Generator & Architecture Wizard)によりクロックを逓倍する回路を作成します.

プロジェクトの新規作成

プロジェクトの新規作成方法はこちらで紹介していますのでご覧ください.今回のプロジェクト名は「Clock」としました.

IPの追加

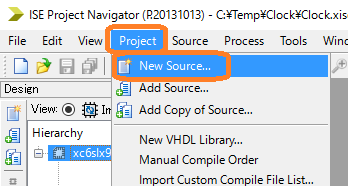

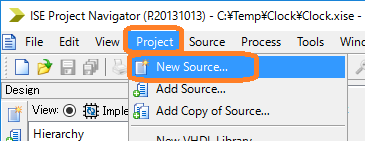

次にIP(CORE Generator & Architecture Wizard)によるクロック管理回路を追加します.まずは下図のようにProject⇒New Source...をたどります.

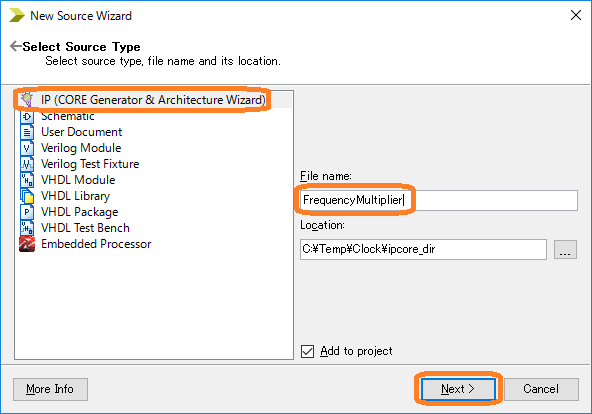

現れたダイアログに対して,「IP(CORE Generator & Architecture Wizard)を選択し,FileNameを「FrequencyMultiplier」としてNextボタンを押します.

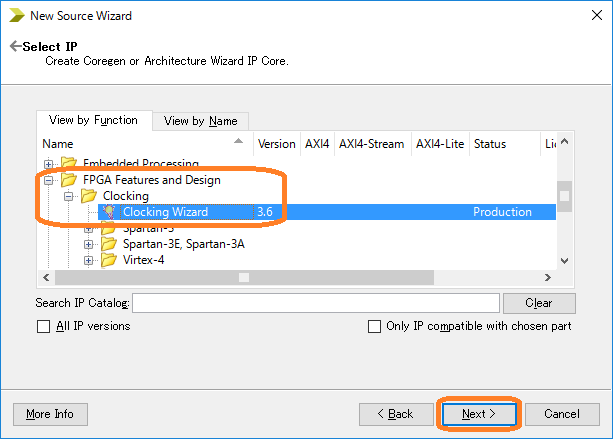

次にIPを選択します.ここでは,FPGA Features and Design ⇒ Clocking ⇒ Clocking Wizardを選択しましょう.

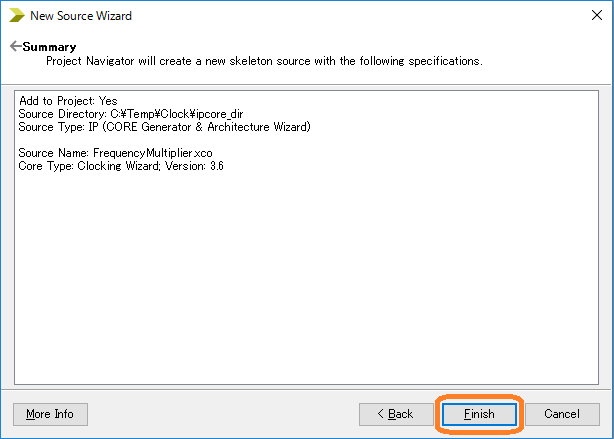

最後に,作成するIPの確認用ダイアログが現れますのでFinishを押してください.

IPの設定ウィザード

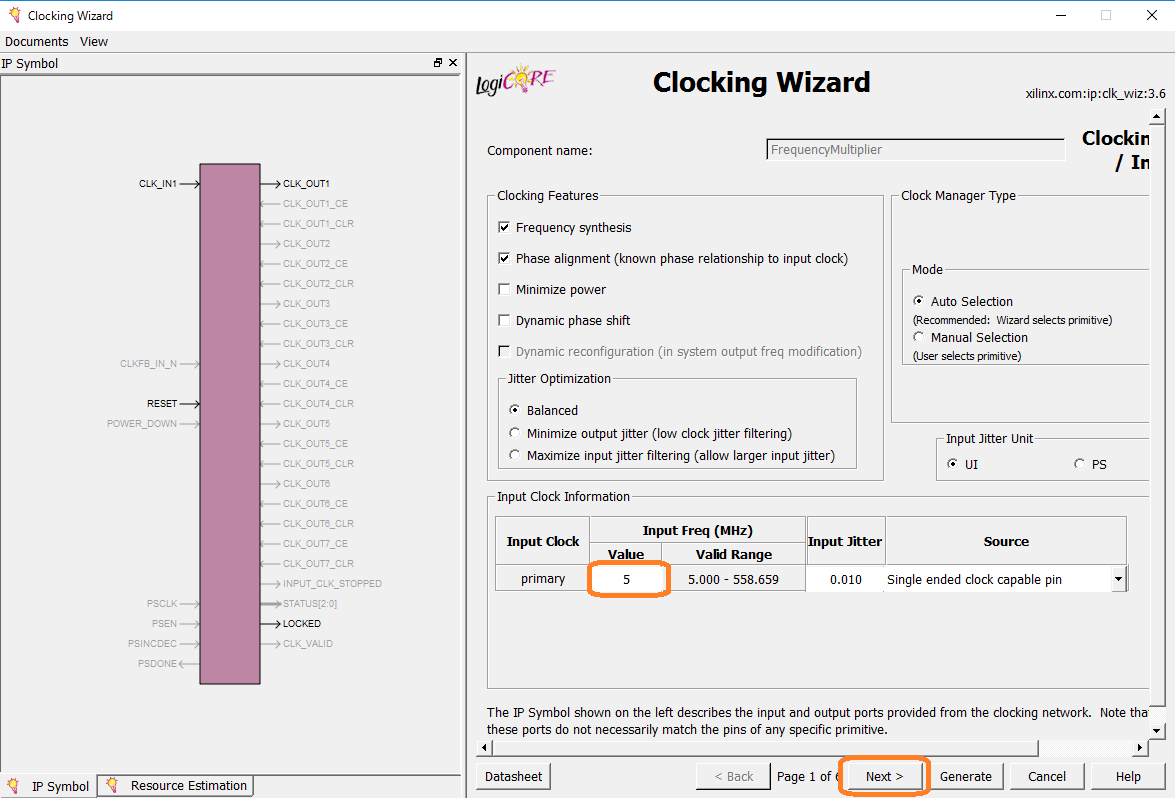

続いてClockの設定をするウィザードがはじまります.最初に入力するクロックの情報を設定します.ここでは最低5[MHz]の周波数となっておりますので,下図のように5と入力してください.

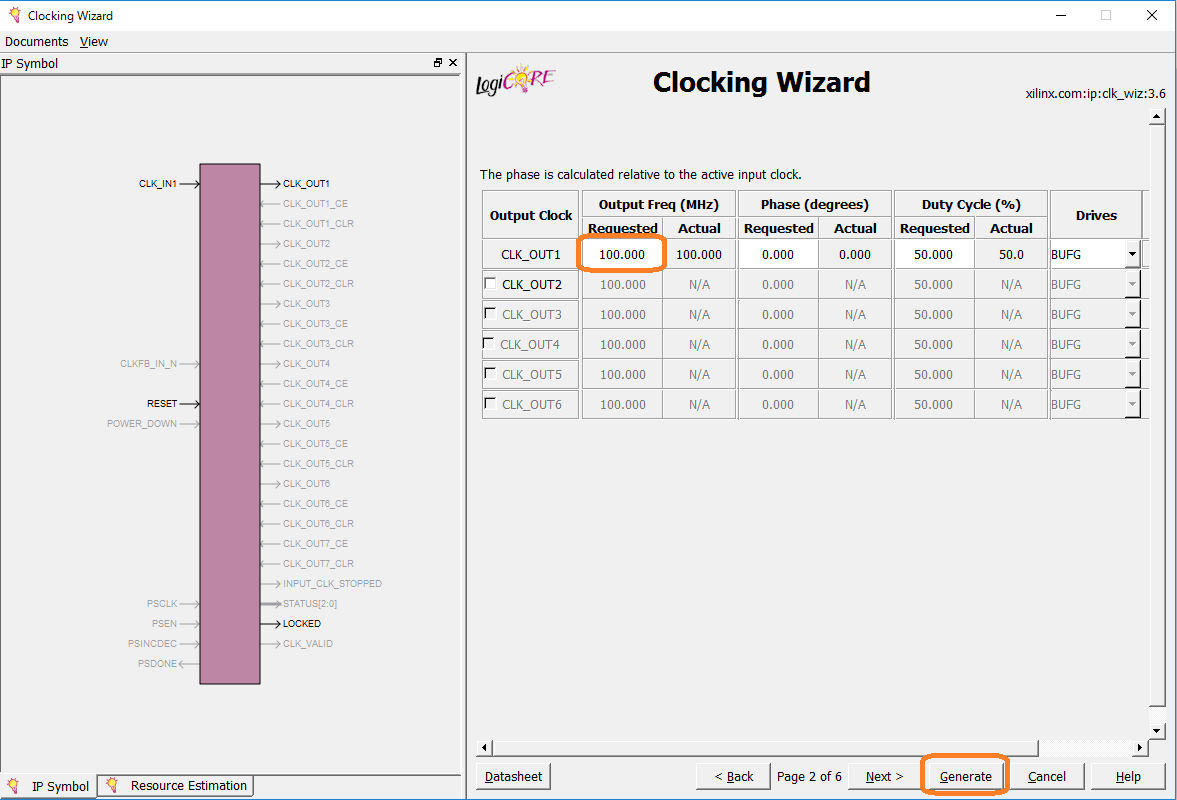

次に(というかこれで最後ですが),出力する波形の周波数を指定します.下図のように今回は100[MHz]とします.この後にまだ細かな設定を行えるのですがそこは省略します.そのためGenerateボタンを押します.

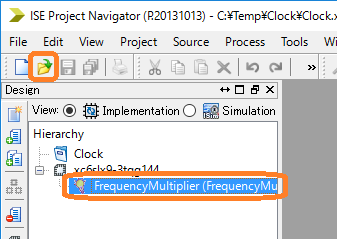

IPが生成されると下図のようになります.続いて,作成された回路を扱うためのVerilogファイルを開き,ポートを確認しておきましょう.下図のようにファイルオープンアイコンを押してください.

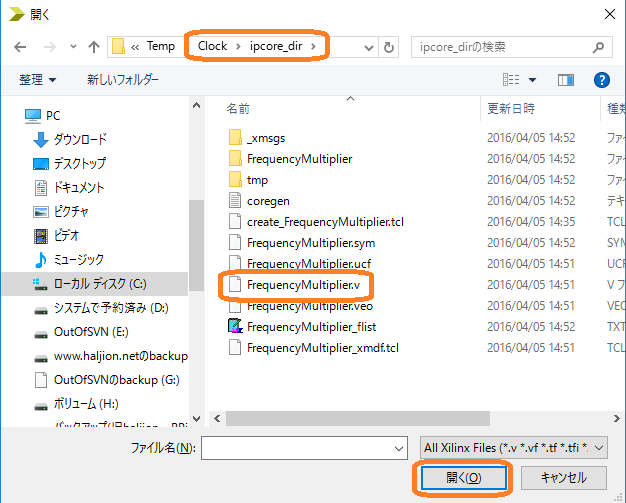

Clockフォルダの下にipcore_dirフォルダがあるはずです.その中にFrequencyMultiplier.vファイルがありますので選択して開くボタンを押しましょう.

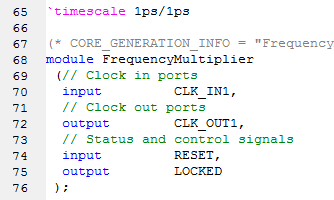

FrequencyMultiplier.vのポート宣言をご覧ください.下記のとおり,4種類のポートがあります.

今回生成されたポートの役割を下表にまとめておきます.

| ポート名 | 入力/出力 | 役割 |

| CLK_IN1 | 入力 | 入力されるソースクロック.5[MHz]を想定している. |

| CLK_OUT1 | 出力 | 出力されるクロック.100[MHz]を想定している. |

| RESET | 入力 | この信号がHighの時にはCLK_OUT1から何も生成されない. |

| LOCKED | 出力 | クロックが正しく出ているときにはHigh,そうでないときにはLowを出力. |

作成された回路の動作確認をするため,テストベンチを作成してみましょう.下図のようにProject⇒New Source...と辿ります.

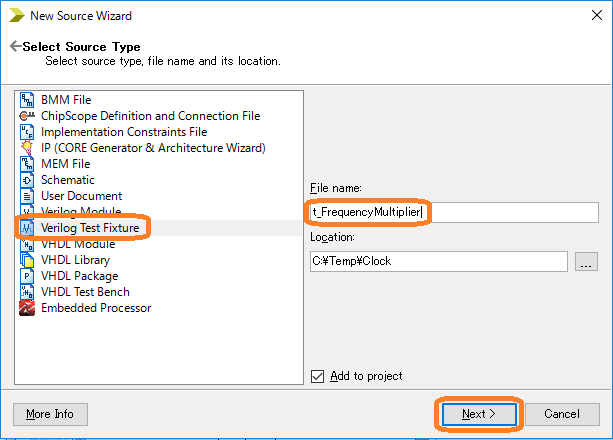

テストベンチを作成するにはVerilog Test Fixtureを選択します.今回のテストベンチ名であるt_FrequencyMultiplierと記入してNextを押します.

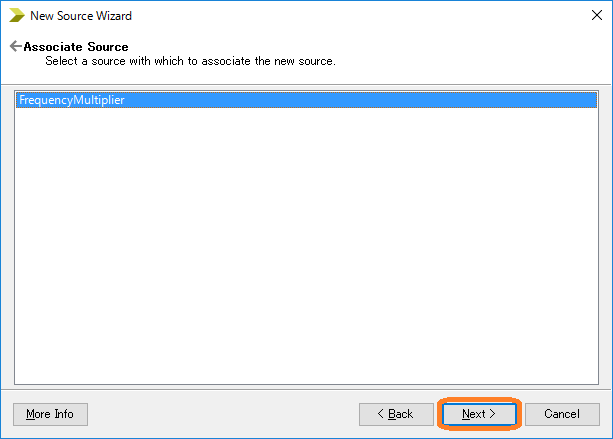

動作確認するモジュールを選択し,Nextを押します.

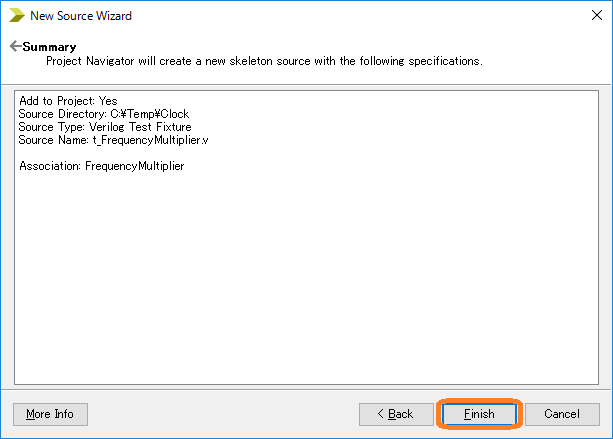

最後に作成するテストベンチの確認を行います.

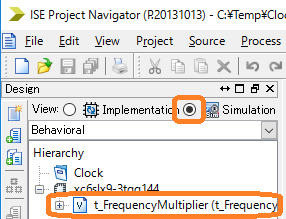

シミュレーションをしますので,下図のようにSimulationを選択しておいてください.

さて,今回作成するテストベンチでは下記のような動作をさせてみます.

- 5[MHz]の周波数,すなわち200[ns]の周期をもつCLK_IN1を永遠に生成する.

- テストベンチ開始後,100000[ns]後にRESETをHighにする.

以上の動作をさせるため,下に示すようなテストベンチを作成します.

module t_FrequencyMultiplier;

// Inputs

reg CLK_IN1;

reg RESET;

// Outputs

wire CLK_OUT1;

wire LOCKED;

// Instantiate the Unit Under Test (UUT)

FrequencyMultiplier uut (

.CLK_IN1(CLK_IN1),

.CLK_OUT1(CLK_OUT1),

.RESET(RESET),

.LOCKED(LOCKED)

);

initial begin

// Initialize Inputs

CLK_IN1 = 0;

RESET = 0;

// Wait 100 ns for global reset to finish

#1000000;

// Add stimulus here

RESET = 1;

end

initial begin

forever begin

#100 CLK_IN1 = 0;

#100 CLK_IN1 = 1;

end

end

endmodule

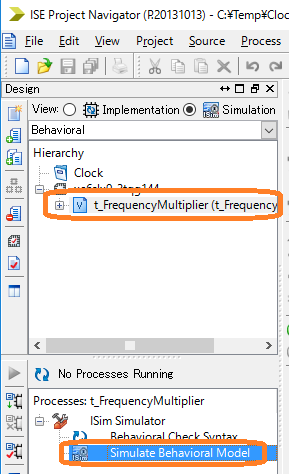

ではシミュレーションで動作させてみましょう.下図のように,t_FrequencyMultiplierを選択したのち,Simulate Behavioral Modelをダブルクリックします.

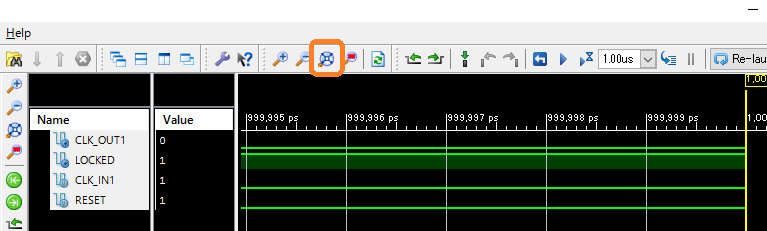

シミュレーションであるISimが立ち上がりますと自動的に1000[ns]だけシミュレーションしてくれます.ただし,そのままだと見づらいので下図のように全体を表示できるアイコンを押してください.

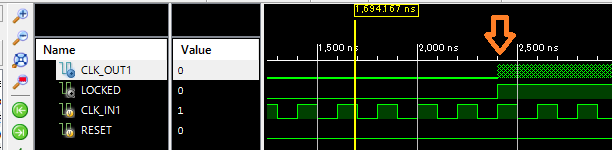

下図は0~3000[ns]までの表示をさせたうちの一部を抜粋したものです.ここでわかることは,CLK_IN1が20[ns]を周期とする信号になっていること,2400[ns]付近でLOCKEDがHighとなり,加えてCLK_OUT1からかなり高い周波数の信号が出ていることが分かります.

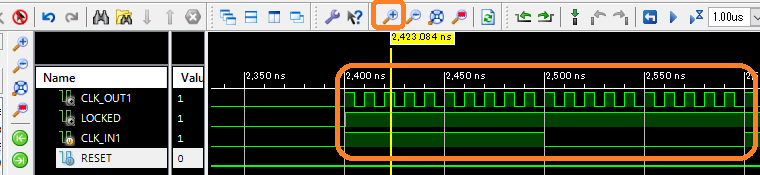

次に240[ns]付近を拡大し,CLK_OUT1を詳細に観察しましょう.下図のようにズームするアイコンを使って2400[ns]付近を拡大してください.すると,CLK_IN1の1周期でCLK_OUT1が20周期あることが確認できました.つまり,CLK_OUT1は100[MHz]であるということです.

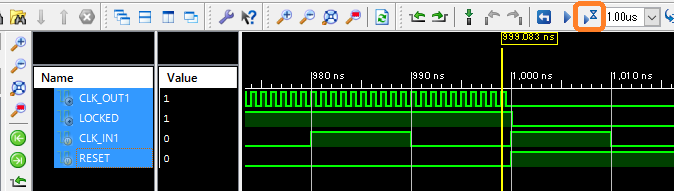

最後に,RESETをHighにした結果どのようになったか確認しましょう.下図のように再生ボタンに砂時計が付いたようなアイコンの左側を1.00msに変えた後,アイコンを1回押してください.これで1[ms]=1000000[ns]だけシミュレーションしてくれます.そして,1000000[ns]付近を拡大してみてみると,ご覧のとおりにRESETがHighになり,その結果,LOCKEDとCLK_OUT1がLowになっている様子が見て取れます.

以上でクロックの逓倍回路の作成方法を終えます.DCMにはこのほかに分周したり,ジッタ(ノイズ)を軽減したりする機能があります.必要に応じて使ってください.