工学実験実習Ⅲでは最後の単元であるA/D変換器の作成についてこの文書では説明します.これまでデコーダでは自ら設計しはんだ付けを行い回路を作成しましたし,セレクタ回路と減算回路ではリバースエンジニアリングをつうじてそれぞれの回路の理解をしてきました.最後のA/D変換器にはさまざまな要素が含まれていますので,ここでは班ごとでブレッドボードに回路を作成することとします.

A/D変換器の回路構成

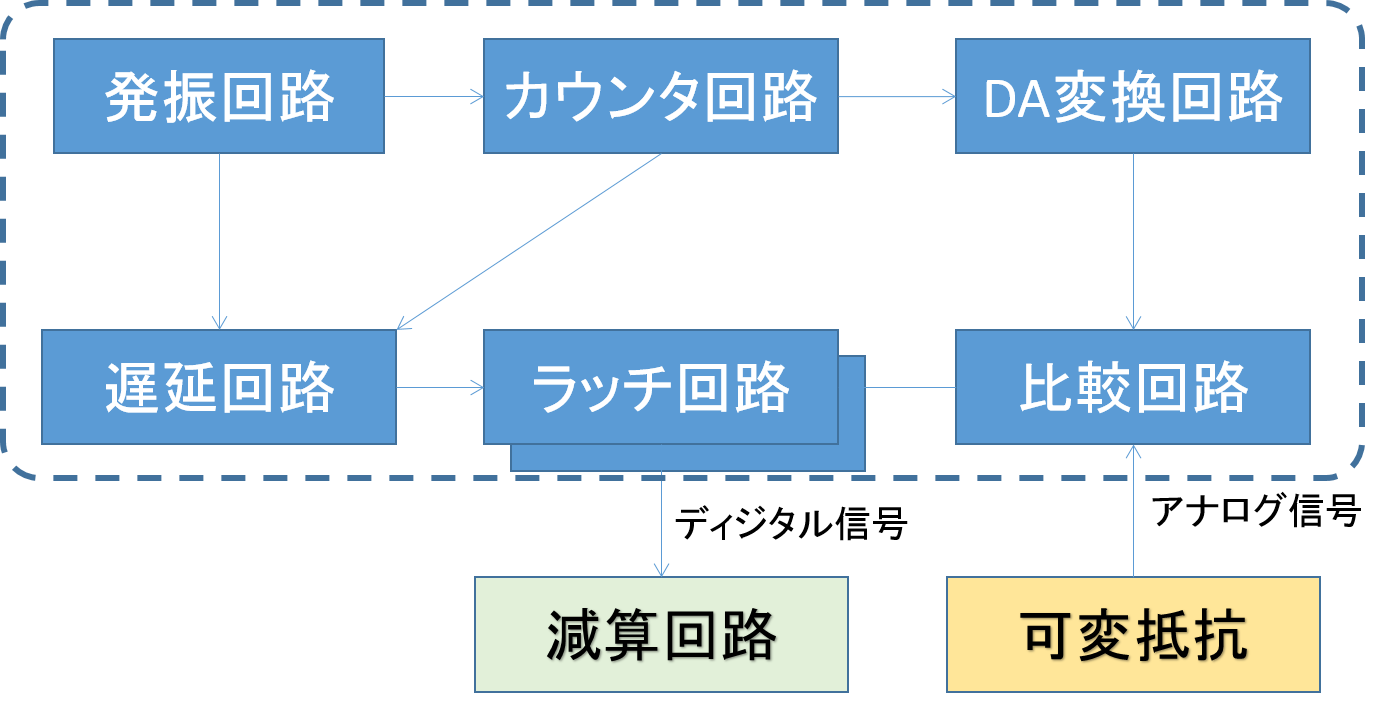

A/D変換器には下に示す7個の回路構成になっています.結構大きな回路になりますので,ブレッドボードの使用面積を抑えながら回路を作成しましょう.

- 無安定マルチバイブレータによる発振器(ユニバーサル基板に作成)

- 3ビットカウンタ(ユニバーサル基板に作成)

- ラダー回路(DA変換回路の一部)

- ボルテージフォロワー回路(DA変換回路の一部)

- 比較回路(コンパレータ回路)

- ラッチ回路による遅延回路

- ラッチ回路

下の図はこれから作成するA/D変換器の概要を表しています.ここではごく簡単に回路全体の動作について説明します.まず発振回路で方形波を生成します.いわゆるクロックです.そのクロックの立ち上がり(ポジティブエッジ)の回数を数えてくれるのがカウンタ回路です.今回は0(0002)から7(1112)までの3ビットで数えます.3ビットの信号をDA変換します.DA変換とはディジタル信号をアナログ信号に変えるものです.アナログ同士では比較できますが,アナログとディジタルの比較はできません.そこで,DA変換回路により,アナログ信号に変換するのです.そして,そのアナログ信号と,可変抵抗によるアナログ信号を比較します.こうすればDA変換回路により得られるアナログ信号はもともとディジタル値でいくつなのか分かっていますので,可変抵抗からのアナログ信号と比較してこちらの方が大きくなったときのディジタル値を捕まえて(ラッチして)減算回路へ送れば,これでAD変換ができるというわけです.下記の図にはこれとは別に遅延回路というものが含まれています.比較回路で可変抵抗のアナログ信号の方が大きくなった瞬間はカウンタのディジタル値が変化する瞬間でもあるため,不安定になってしまいます.そこで,比較結果から少しだけずらしたときのカウンタのディジタル値を得るため,遅延回路があります.

無安定マルチバイブレータによる発振器

無安定マルチバイブレータとは,ずっと一状態にとどまらないマルチバイブレータですので,つまりオンとオフをずっと繰り返している回路といえます.マルチバイブレータには反対に一度だけオンとオフをした後,オフに成りっぱなしとなる単安定マルチバイブレータもあります.こちらはワンショット・マルチバイブレータという時もあり,チャタリングを防ぐために用いられます.チャタリングは一定時間内にオンとオフを断続的に繰り返してしまう現象ですので,ワンショット・マルチバイブレータを用いれば最初の変化からある一定時間まではずっとその状態を保持し続け.その後元の状態に戻るため,チャタリングを起こしている間の変化をやり過ごすことができるからです.

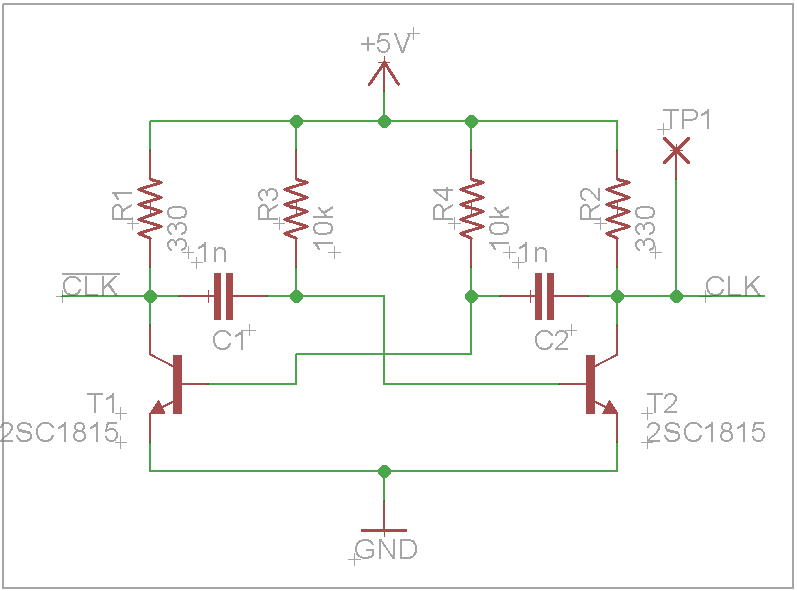

下の回路図はトランジスタを用いた無安定マルチバイブレータです.配線がクロスしているので少しわかりづらいですが,シンメトリに電子部品が接続されています.

この回路により得られる方形波の周波数fは,抵抗R3,R4,静電容量C1,C2で決まります.もし,R3とR4が等しく,C1とC2が等しい場合,それぞれの値をRとCとおくとfとの関係は下に示す式のようになります.

{jmimetex}f=\frac{1}{T}=\frac{1}{ln(2)\cdot 2RC}\approx \frac{0.721}{RC}{/jmimetex}

発展問題

なぜ上記のようなことになるのか調べてください.

無安定マルチバイブレータを作成するには次に示す電子部品が必要となります.抵抗ごとに部品用皿に入っているはずですが,まれに違う部品が含まれていますので,特に抵抗についてはカラーバーを読んで抵抗値を調べてください.

| 部品の種類 | 部品記号 | スペック |

| 炭素被膜抵抗 | R1,R2 | 330[Ω],誤差5%,1/4[W] |

| 炭素被膜抵抗 | R3,R4 | 10[kΩ],誤差5%,1/4[W] |

| 積層セラミックコンデンサ | C1,C2 | 0.1[uF] |

| NPN型トランジスタ | T1,T2 | 2SC1815 |

トランジスタの使い方

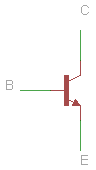

今回使用する2SC1815はNPN型のバイポーラトランジスタで,リード(いわゆる足)はベース[B],エミッタ[E],コレクタ[C]の3本です.回路図ではそれらが下に示すようにあらわします.なお,矢印の向きが外側を向いているのがNPN型,反対に内側に向いているのがPNP型です.

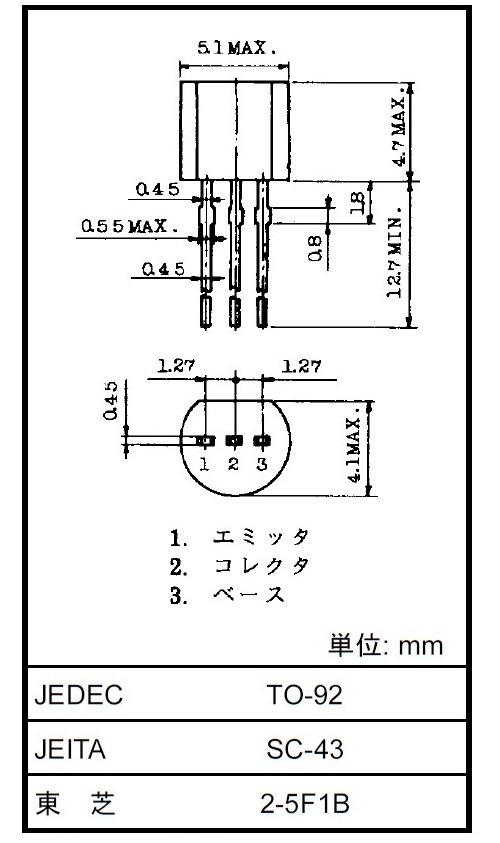

これらのピンアサインはデータシートによると下の図のようになっています.中段あたりにある図は,2SC1815を下から見た図です.見る向きで逆になってしまいますので注意してください.

※上記の図は2SC1815のデータシートの一部です.

2SC1815の写真でピンアサインを示しますと下のようになります.左側のリードからE,C,Bの順番になっています.多くのトランジスタではこの並びになっているため,慣れた人だとECBを「エクボ」と覚えるそうです.しかし,絶対にこのアサインであるとは限りませんので,やはり最終的にはデータシートを必ず見るようにしてください.

実験と報告

上記の回路図にもとづき回路を作成してください.そして,TP1の位置(CLK)をオシロスコープで観察しましょう.観察した波形は方形波になっているはずです.この方形波の周波数を調べてください.理論値との違いもチェックしてください.また,{jmimetex}\overline{CLK}{/jmimetex}もあわせて観測してください.TP1と{jmimetex}\overline{CLK}{/jmimetex}は逆位相の関係になっているはずです.

観測した図は,手書きもしくはgnuplotなどで描画してください.オシロスコープにあるキャプチャリング機能で撮影したものをレポートに用いないでください.gnuplotなどで描く場合,観測した波形をデータ化し,CVS形式で出力する機能をオシロスコープは備えていますので,その機能を使ってデータを取得してください.複数の波形を一つの図で示すとき,必ず縦方向に分けるようにしてください.この理由は,複数の信号を重ねて描画してしまうと,仮に信号ごとに線の種類が違っていても分かりづらくなるからです.なお,このように縦方向を電圧,横方向を時間とし,複数の信号を縦に並べてそれぞれの関係を表す図のことをタイミングチャートといいます.

無安定マルチバイブレータとカウンタ回路はユニバーサル基板に作成します.この場合,実体配線図を作成してからはんだ付けを行ったほうが確実に動作する回路を作成できます.ユニバーサル基板のための実体配線図を作るときに使う資料をこちらに置いておきます.

3ビットカウンタ

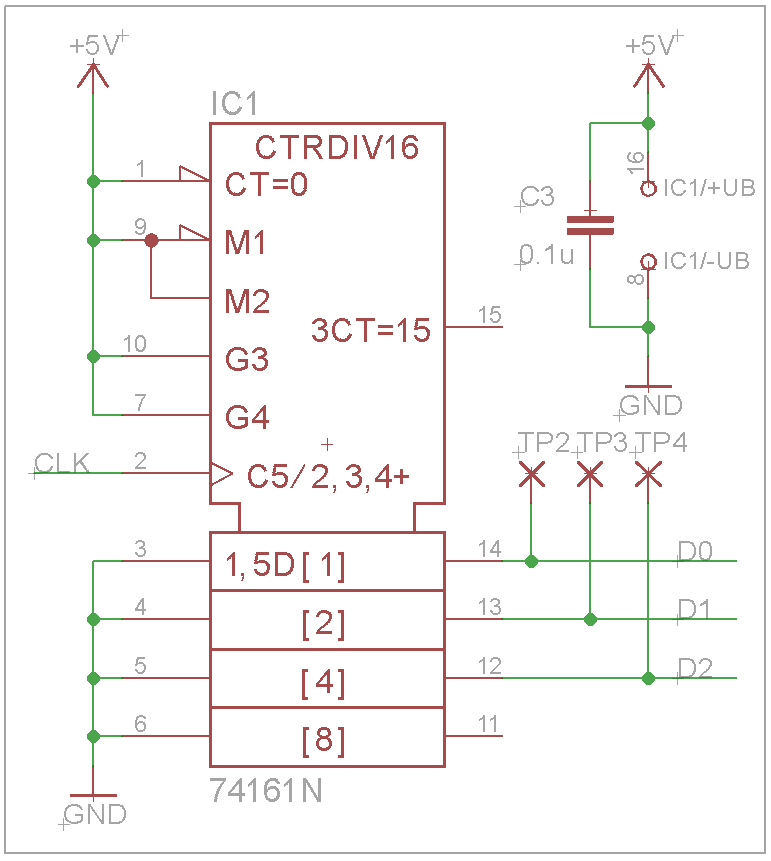

次に3ビットカウンタを作成します.といっても,すでにあるカウンタ回路74HC161を使いますのでそれほど難しくありません.このICのには4個のフリップフロップが含まれており,4ビットまでの信号を数えることができます.従いまして,最上位1ビットは使われません.下の図には74HC161の接続方法が描かれています.

注意しなければいけないことは,このICが74HCシリーズであるということです.デコーダ,セレクタおよび減算回路はすべて74LSシリーズだったのですが,これだけは74HCにしてあります.74LSシリーズはTTLでできており,電流駆動型ですが,74HCシリーズはCMOSでできており,電圧駆動型です.従いまして,少しの電圧的変化でも動作が不安定になってしまいます.ということは,バイパスコンデンサが重要になるということです.もし正しくカウントしてくれないようであれば,バイパスコンデンサの位置をなるべくICの電源に近づけたり,バイパスコンデンサの静電容量を変更してみてください.

実験と報告

上記の回路図にもとづき回路を作成してください.そして,CLK(TP1),TP2,TP3,TP4の4信号をオシロスコープで観測してください.発振器の報告と同様,タイミングチャートを描くときには各信号を重ねることなく縦に並べるようにしてください.

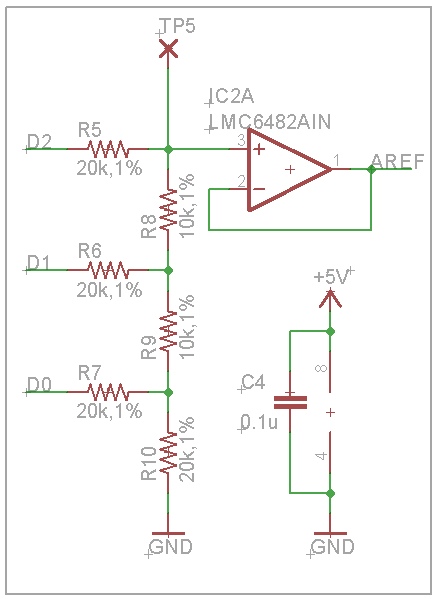

ラダー回路

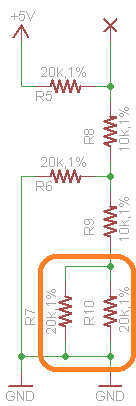

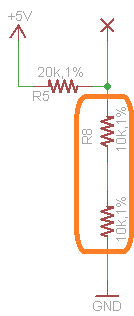

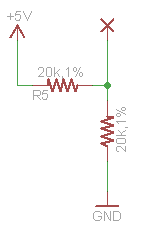

カウンタ回路により3ビットのディジタル信号D2~D0が出力されますので,今度はこれをアナログに変換しましょう.まずはラダー回路です.「ラダー」とは縄梯子のことで,下に示す回路図の左側に集まっている抵抗の配置が縄梯子に似ているためです.今回は3ビットしかないため,言ってみれば3段のはしごとなっています.

さて,TP5の電圧がアナログ回路になっているのですが,なぜそのようになるのか考えてみましょう.事前に抵抗値を確認してください.よく見るとR5,R6,R7,R10が20[kΩ],R8,R9が10[kΩ]となっています.大事なのはこの比率です.つまり,R5をはじめとする抵抗群と,R8の抵抗群の比率が2対1になっていればこの回路は成立します.従いまして,R5の抵抗群が1[kΩ],R8の抵抗群が500[Ω]でもよいということです.

では実際に計算をしてみましょう.ここでは例としてディジタル値1002をアナログ値2.5[V]となることを説明します.1002ということは,D2=High,D1=Low,D0=Lowとなります.これを回路図にすると下のようになります.

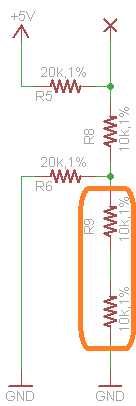

この回路を少し変形すると下のようになるのがわかるでしょうか.

R7とR10が並列に並んでいることが分かりますね.従って,R7とR10の合成抵抗R[kΩ]は下のようになります.

{jmimetex}R=\frac{1}{\frac{1}{20}+\frac{1}{20}}=\frac{1}{\frac{2}{20}}=\frac{20}{2}=10{/jmimetex}

以上のように10[kΩ]となりますので,上の回路は下のように変形できます.

今度はR9とRが直列に接続されていますので合成抵抗は20[kΩ]となります.従いまして,さらに下のように変形できます.

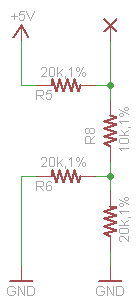

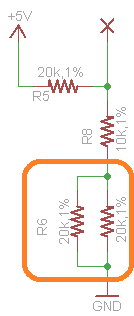

グランド付近に注目してみると,また前のように20[kΩ]の抵抗が並列に接続されていることが分かります.下に変形した様子を示します.

20[kΩ]の抵抗が並列に接続されていますので,合成抵抗は10[kΩ]となります.従って下のように変形できます.

今度は10[kΩ]の直列接続ですので,合成抵抗は20[kΩ]となり,最終的に下のような回路となります.

この回路を眺めますと,20[kΩ]の抵抗が2個あり,その真ん中の電圧を測ればよいことが分かります.この場合,分圧すればよいので下の式のようになります.

{jmimetex}V=5\times\frac{20}{20+20}=5\times\frac{1}{2}=2.5{/jmimetex}

このように,TP5の電圧は2.5[V]であることが分かります.繰り返しますが,今回は20[kΩ]と10[kΩ]を使いましたが,2RとRの抵抗値を持つ抵抗なら上記の計算を同じように求めることができます.

実験と報告

ラダー回路をブレッドボード上に作成し,TP5をオシロスコープで観測してください.また,D2~D0は理想的な場合には下記の表のような電圧となります.観測したものと比較してください.さらに,D2~D0が下表のようになることを証明してください.このとき,式を省略せずに書いてください.

| D2 | D1 | D0 | 電圧値 |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0.625 |

| 0 | 1 | 0 | 1.25 |

| 0 | 1 | 1 | 1.875 |

| 1 | 0 | 0 | 2.5 |

| 1 | 0 | 1 | 3.125 |

| 1 | 1 | 0 | 3.75 |

| 1 | 1 | 1 | 4.275 |

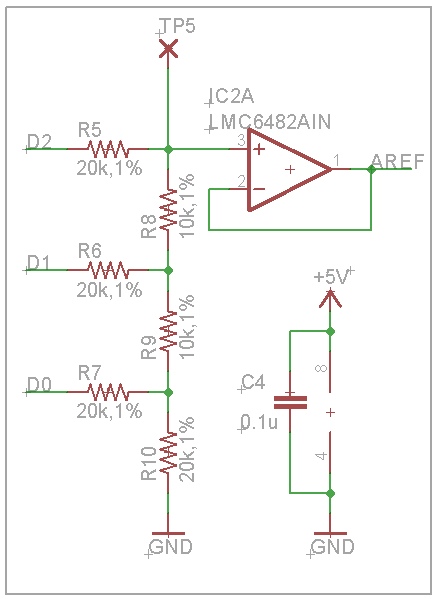

ボルテージフォロワー回路

ラダー回路によりディジタル値をアナログ値に変換できましたので,さあコンパレータ回路で…と行きたいとこなのですが,その前にボルテージフォロワー回路に通す必要がります.なぜこの回路が必要かというと,ラダー回路はある程度大きな抵抗になっているためあまり電流が流せないからです.流せないということは電圧降下が発生してしまうこととなり,電圧がくるってしまうということになります.そこでボルテージフォロワー回路が必要となります.この回路にはオペアンプを用いますがオペアンプの入力端子の抵抗値は非常に高くほとんど電流を流す必要がありません.このため,ラダー回路の出力電圧を下げることはほぼありません.

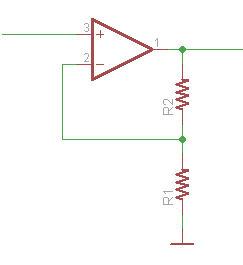

下の図はオペアンプの動作を説明するためのものです.

オペアンプにはいろいろな使い方がありますが,下のものは非反転増幅回路といわれるもので,R1とR2の抵抗値で電圧を増幅してくれます.入力の電圧をVI,出力の電圧をVOとしたとき,下の式のようになります.

{jmimetex}V_O=(1+\frac{R_2}{R_1})V_I{/jmimetex}

ボルテージフォロワーの場合,R2=0,R1=∞となった場合と考えられますので,分数の箇所が0となり,VO=VIとなります.

実験と報告

下の回路図にもとづき回路を作成してください.そして,TP5とAREFをオシロスコープで同時に観測して比較してください.

アナログ信号の生成

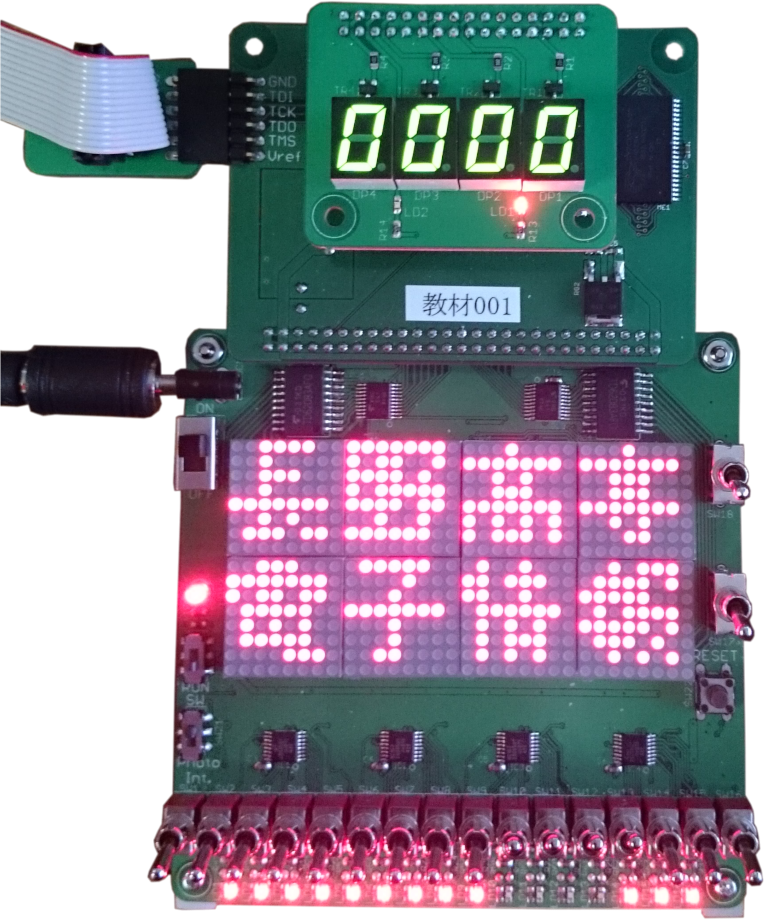

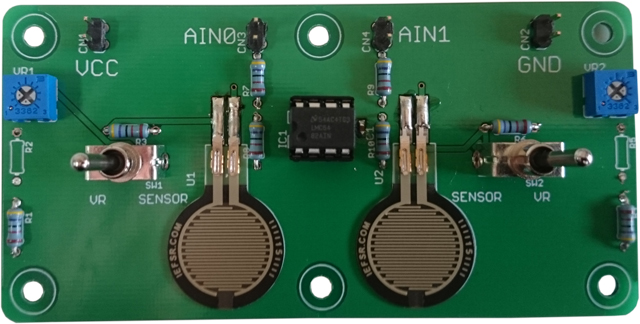

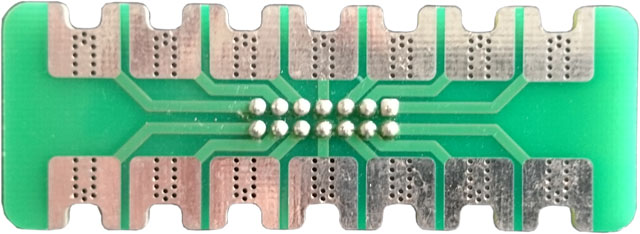

一旦本筋から外れて,ここではアナログ信号を生成する回路について説明します.下にあるのがアナログ信号を生成するための基板です.端子が上に4個あり,左からVCC(5[V]),AIN0,AIN1,GND(0[V])となっています.VCCとGNDを接続することでこの回路は動作し,AIN0とAIN1からアナログ信号が出てきます.アナログ信号の電圧を調整する方法は2種類あり,一つが可変抵抗器,もう一つが圧力センサによります.この切り替えには中段にあるトグルスイッチで行います.

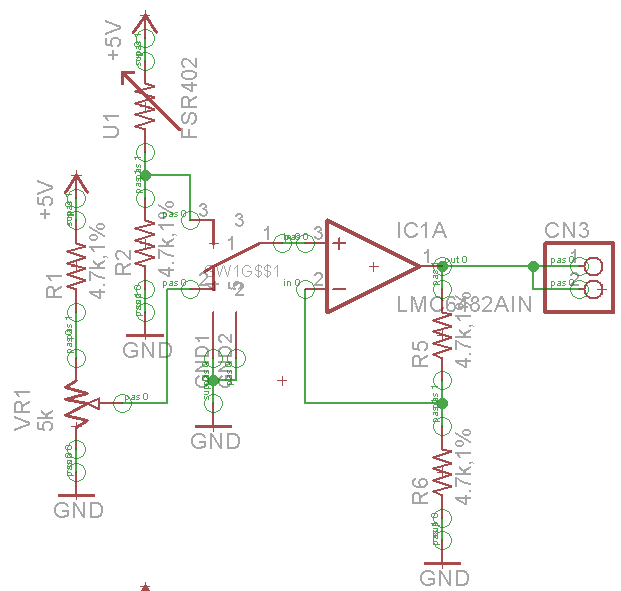

下の図は,アナログ信号を生成する回路図を抜粋したものです.VR1が可変抵抗器,U1が圧力センサです.ともに0~2.5[V]程度の電圧を出力するようになっています.それらの信号を中央付近にあるスイッチで切り替えることができるようになっており,後段のオペアンプに接続されています.このオペアンプはボルテージフォロワーでも使っているLMC6482AINです.今回は2倍に増幅するため,R5とR6が同じ抵抗値となっています.

確認

VCCとGNDを接続し,AIN0とAIN1の電圧をテスタで確認してください.

コンパレータ回路

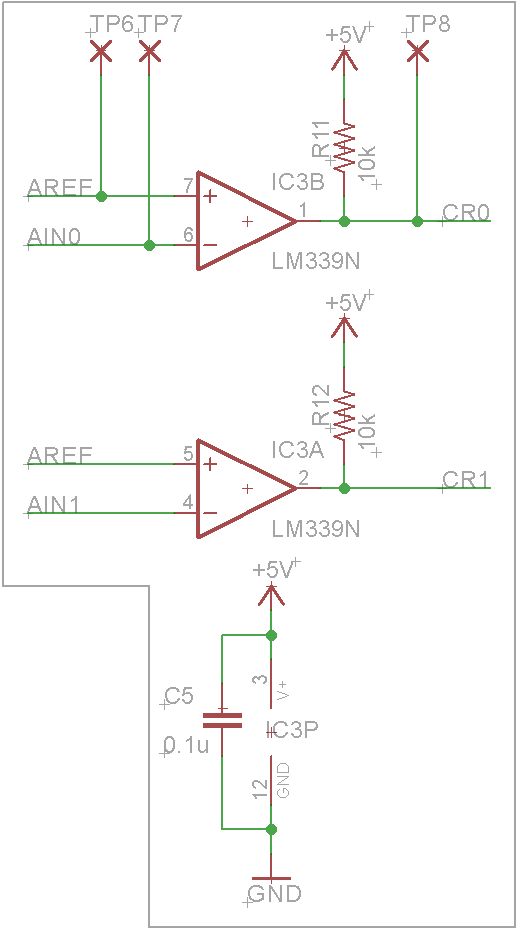

コンパレータでは,ボルテージフォロワー回路から得られた信号をAREF,可変抵抗器もしくは圧力センサから得られた信号をAIN0とAIN1をコンパレータで比較します.使用するLM339Nには2個のコンパレータが入っていますので,1個のICで下記の回路を作成します.

コンパレータは記号のとおり,内部的にはオペアンプとなっております.非反転入力(V+)と反転入力(V-)を比較したとき,V+の方が大きければVS+(今回は5[V])となり,V-の方が大きければVS-(今回は0[V])が出力されます.そしてCR0とCR1につながります.

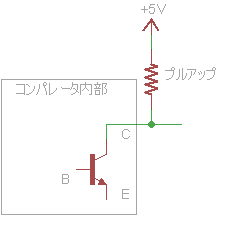

ここで注意しなければならないのは,コンパレータの出力はオープンコレクタになっておりますので,プルアップする必要があります.ここで,オープンコレクタとはコレクタがIC内部では接続されていない状態のことを言います.このため,IC外部にプルアップ抵抗をつけてあげる必要があります.下の図はその模式図です.このようにプルアップしないと出力端子からHighでもLowでもない信号が出てしまうことがお分かりいただけると思います.

実験と報告

コンパレータ回路を作成し,TP6,TP7,TP8をオシロスコープで観測し,スケッチをしてください.可変抵抗器を変化させてTP7を0から5[V]までの変化をさせ,どのタイミングでTP8が変わっていくことを確認して表にまとめてください.

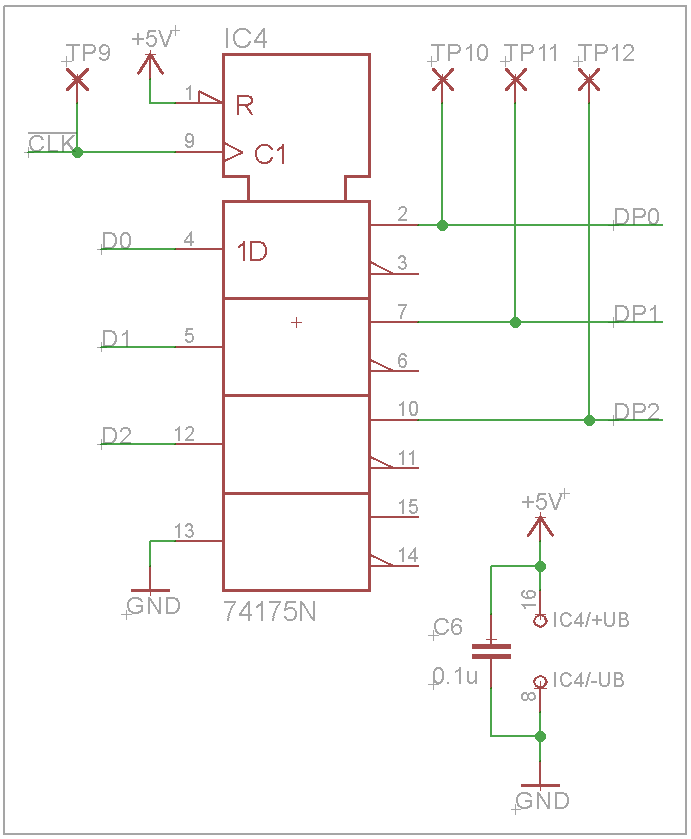

ラッチ回路による遅延回路

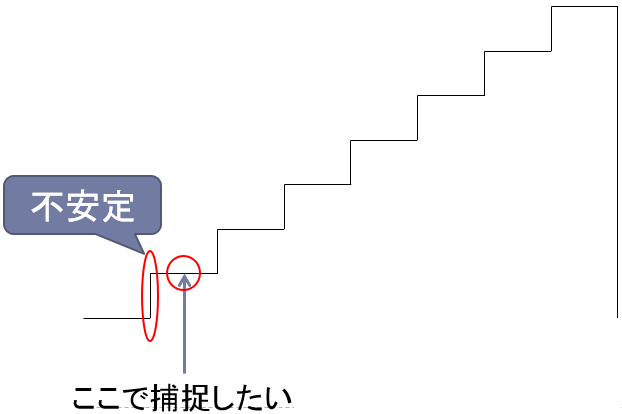

コンパレータ回路から出力される信号の立ち上がりエッジで,カウンタ回路の出力信号をラッチしてしまうと,過渡期であるためどちらか判断できないカウンタの出力信号をラッチしてしまうことになってしまいます.下の図は,階段の波形がボルテージフォロワー回路の出力の模式図です.ご覧のとおり階段の立ち上がりのタイミングにコンパレータ回路の変化がするため,階段の下の段なのか,上の段なのか,わからなくなってしまうということです.そこで,少し時間を遅らせる必要があります.

そこで登場するのが遅延回路です.遅延回路を作るのに,色々な方法がありますが,今回はラッチ回路を使うこととします.ラッチ回路とはあるタイミングで信号を取りおいてくれる回路です.遅延回路を作成するにはあるタイミングを{jmimetex}\overline{CLK}{/jmimetex}の立ち上がりエッジ,取りおく信号をカウンタ回路の出力とします.なぜこのようにしているのかというと,上記の図でいう階段の踊り場の真ん中がちょうど{jmimetex}\overline{CLK}{/jmimetex}の立ち上がりになっているからです.

実験と報告

遅延回路を作成し,TP9とD0とTP10(DP0),TP9とD1とTP11(DP1),TP9D2とTP12(DP2)をオシロスコープで観測してください.信号がTP9を基準に遅延していることを確認してください.

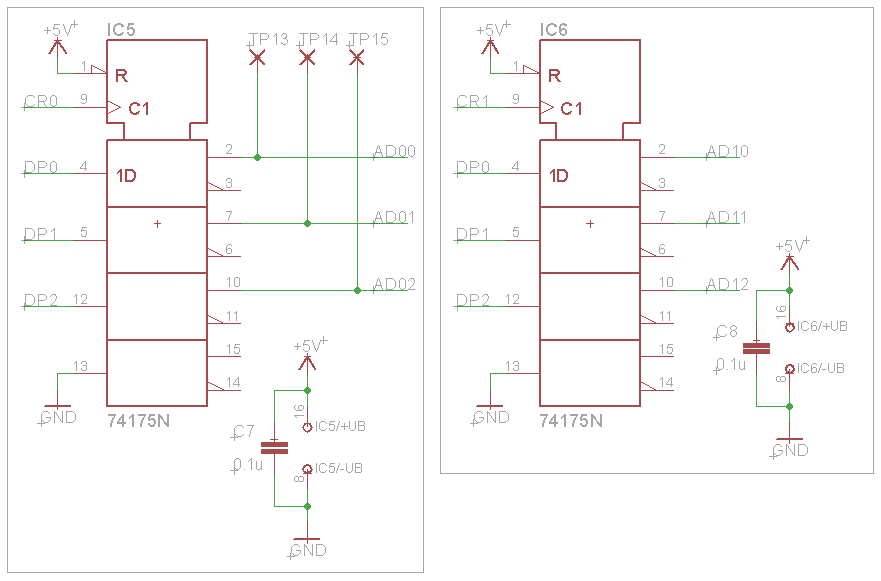

ラッチ回路

最後はラッチ回路です.このラッチ回路では,取り込むタイミングをコンパレータの出力であるCR0とCR1,取りおく信号として遅延回路の出力です.そして,ラッチ回路の出力を減算回路へ送るようにします.

出力であるAD00~02,AD10~12を減算器に送るには,減算器に備わるピンヘッダJ1と接続します.そのためのピンアサインを下表に示します.簡単に説明するとAD00~12がA,AD10~AD12がBとなるようにして下さい.

| ピン番号 | 信号名 |

| 1 | VCC |

| 2 | AD02 |

| 3 | VCC |

| 4 | AD01 |

| 5 | VCC |

| 6 | AD00 |

| 7 | VCC |

| 8 | AD12 |

| 9 | GND |

| 10 | AD11 |

| 11 | GND |

| 12 | AD10 |

| 13 | GND |

| 14 | GND |

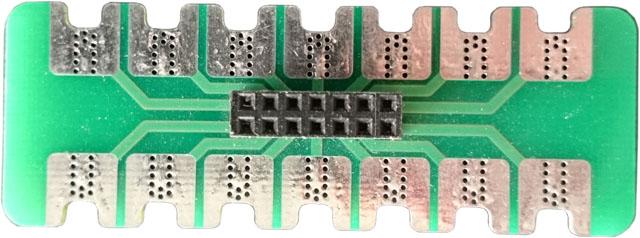

上記のように減算器のJ1に接続するときに使えるのがピンヘッダ拡張用端子台(下図は表側と裏側)です.これをJ1端子に設置し,ワニ口クリップでAD00などの信号と接続します.

実験と報告

可変抵抗器もしくは圧力センサを変化させ,ラッチ回路の出力であるAD02~0,AD12~0がともに000から111に変化するか確認してください.また,減算回路,セレクタ回路およびデコーダ回路を接続し,電子天秤を完成させて動作を確認してください.最後に,今回作成した逐次比較型AD変換器以外のAD変換器について書籍で調べて報告してください.