Page 8 of 9

ラッチ回路による遅延回路

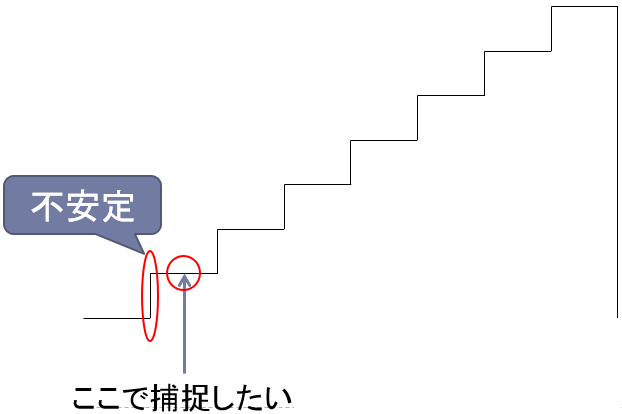

コンパレータ回路から出力される信号の立ち上がりエッジで,カウンタ回路の出力信号をラッチしてしまうと,過渡期であるためどちらか判断できないカウンタの出力信号をラッチしてしまうことになってしまいます.下の図は,階段の波形がボルテージフォロワー回路の出力の模式図です.ご覧のとおり階段の立ち上がりのタイミングにコンパレータ回路の変化がするため,階段の下の段なのか,上の段なのか,わからなくなってしまうということです.そこで,少し時間を遅らせる必要があります.

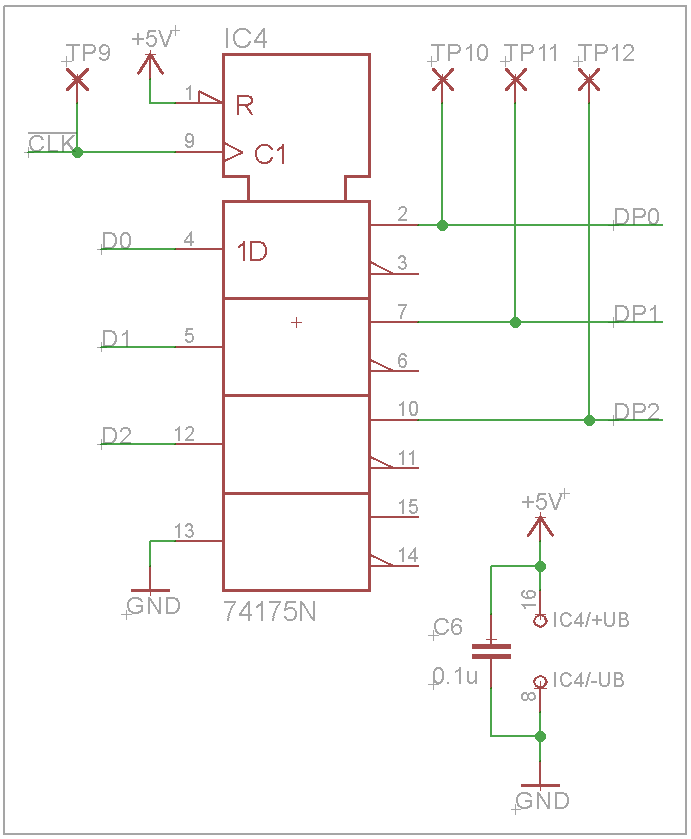

そこで登場するのが遅延回路です.遅延回路を作るのに,色々な方法がありますが,今回はラッチ回路を使うこととします.ラッチ回路とはあるタイミングで信号を取りおいてくれる回路です.遅延回路を作成するにはあるタイミングを{jmimetex}\overline{CLK}{/jmimetex}の立ち上がりエッジ,取りおく信号をカウンタ回路の出力とします.なぜこのようにしているのかというと,上記の図でいう階段の踊り場の真ん中がちょうど{jmimetex}\overline{CLK}{/jmimetex}の立ち上がりになっているからです.

実験と報告

遅延回路を作成し,TP9とD0とTP10(DP0),TP9とD1とTP11(DP1),TP9D2とTP12(DP2)をオシロスコープで観測してください.信号がTP9を基準に遅延していることを確認してください.